If she manages to save the semicon industry and lets some valid latin IC houses work better with Leuven and Eindhoven, she will definitely have earned her creds to a PM position. Is that even possible with the current european governancy glued in inter-nation bickering about the ants and the krekels and the ex-commies with lack of direct democracy or means of action ? ... let me get back to my technical daydreamings on dive computers. Less depressing.I'm really a fan of Neelie Kroes, though. She should stop wasting her time in Europe and run for PM this time around so the Dutch get a real leader in "het torentje" at least once in a generation.

The point being that my previous point about KISS applies every bit as much to building IC's as it does to building software. Putting more and more functionality into an IC will make the process of development and testing exponentially more difficult (as the ITRS discovered in its roadmapping efforts) and the reliability will not be improved in the process. The *last* step, printing it on silicone, doesn't change in any significant way but that's not the step where the risk is and that's not the step where chip manufacturers make major logic/design decisions.

Yes. The not well thought out More than Moore and the rush to multi CPU looked like desperate attemps to wiggle away when the horizon of atomic variability and thermal wall approaches. When it hits the fan, the boel will have to be picked up by software, which has been running on free fuel for more than 40 years.

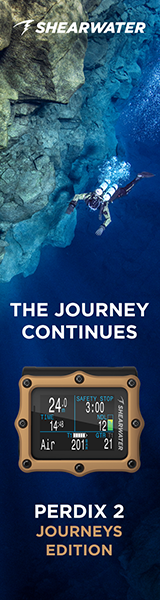

What I *do* foresee is integration of smartphones or computers with dive computers (via the cloud) so that important dive information like profiles and deco schedules can be up/downloaded seamlessly without cables and all that "nerdy" work we have to do today.

Ah ha. So you do have some new feature for tec in mind: downloading the tables calculated during planning on PC or phone to the DC. So the DC would act like a backup printed table, or would it still have some reactiveness ( like switching to another precalculated table because of 1m depth or 1mn time skew. Or even entering the "realtime" mode when the profile has gone way off.) ?

So, yes. I would agree with you that *IF* we were to build one architecture for all dive computers that it should be able to talk to a transmitter.

Where we differ is that I believe that building one architecture to cover all the bases isn't usually the most productive direction. I can see it from a chip manufacture's perspective. They don't want to have to manufacture 600,000 different chips. From the perspective of a dive computer manufacturer or a diver, however, it's really an esoteric discussion that doesn't make any sense.

Why is volume a benefit for the wafer pusher only ? The development house will dilute their NRE costs in those volumes too, and their tests and verifications plans need not necessarily explode (exp grow). And for the diver has has in the end cheaper hardware so his money is available to other priorities. Anyway we can not go further on settling this without first putting proper numbers behind.

Integrating wireless on the logic die is tricky, that is true. But normally it is only the RF that will suffer from spurious, not the logic (good new for the deco calculation, bad news for the number of respins).

If you think the discussion is too obscure for most SB readers, we can stop it here. This was a pleasure having it go so far.